引言

CDSP SW(Converter Digital Signal Processor software)是专用于TC4x CDSP 硬件模块的软件包。

CDSP SW 以二进制文件和头文件提供,用户通过配置参数并将其存储在 CDSP 的 DCCM 中来实现特定的滤波功能,通过将指令二进制代码存放在CDSP的ICCM来实现算法,在 TriCore™ 核上运行的应用程序无需调用API 即可实现 CDSP SW 的滤波功能来对外部输入信号进行处理。

Jan . 2025

分享至

CDSP SW(Converter Digital Signal Processor software)是专用于TC4x CDSP 硬件模块的软件包。

CDSP SW 以二进制文件和头文件提供,用户通过配置参数并将其存储在 CDSP 的 DCCM 中来实现特定的滤波功能,通过将指令二进制代码存放在CDSP的ICCM来实现算法,在 TriCore™ 核上运行的应用程序无需调用API 即可实现 CDSP SW 的滤波功能来对外部输入信号进行处理。

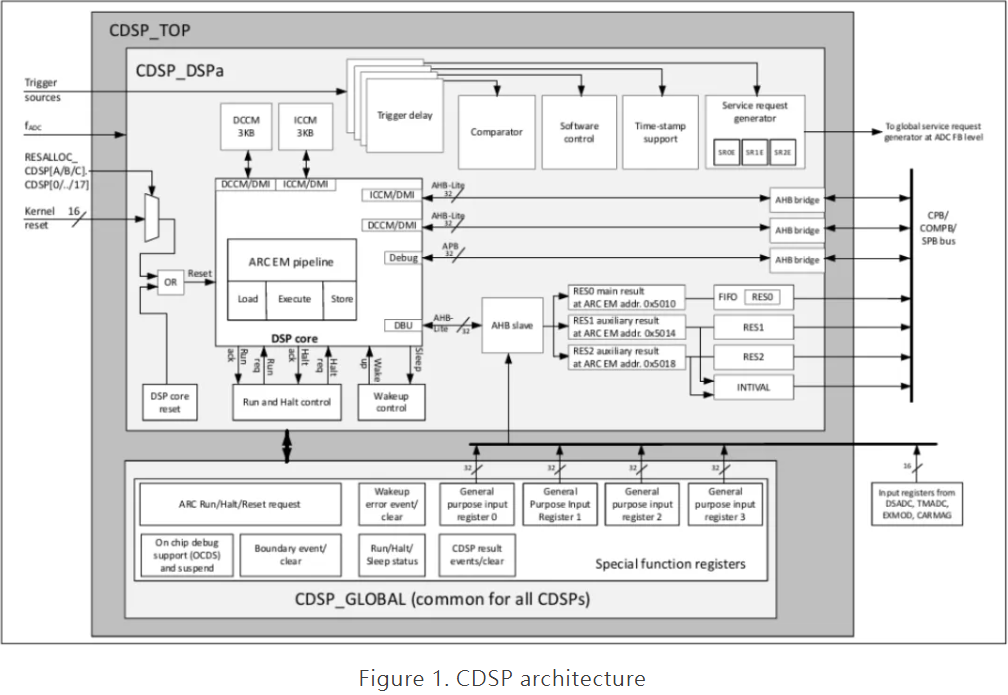

CDSP包括一个 Synopsys DesignWare® ARC® EM5D(ARC) DSP 内核,3 KB 指令存储器 (ICCM)、3 KB 数据存储器 (DCCM) 。

CDSP 以 f_ADC频率运行(160MHz), CDSP作为一个外设,由Tricore控制其复位、运行等。

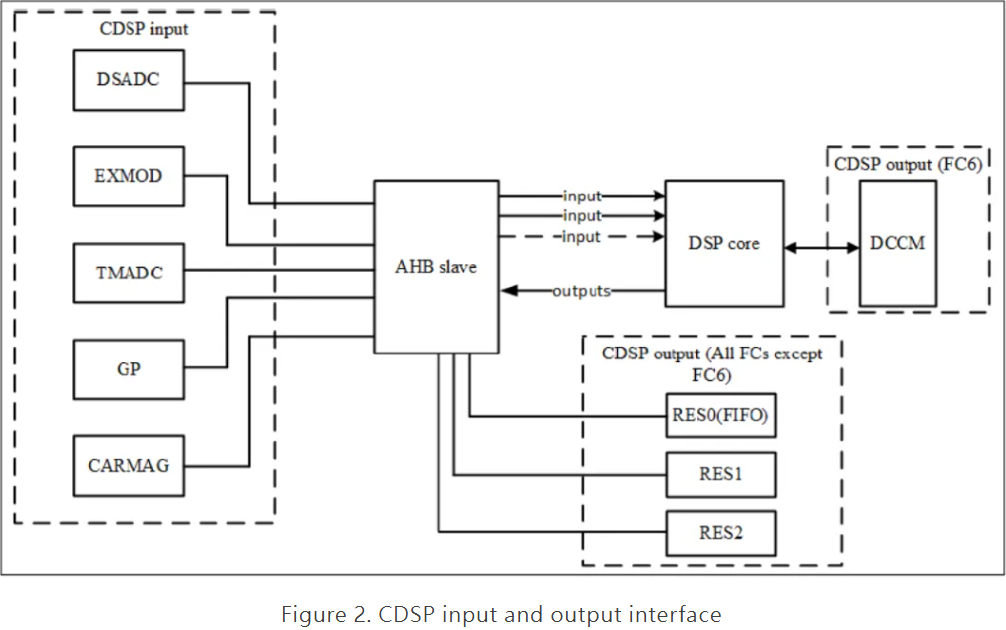

CDSP可以处理来自DSADC (Δ-Σ ADC)、EXMOD (外部调制器)、TMADC (分时复用 ADC)、CARMAG (载波调制器) 或GP (通用) 寄存器的信号。

CDSP处理完成,产生的结果存放在结果寄存器RES0,RES1和RES2或DCCM,并且RES0有一个深度为4的FIFO用于结果缓存。

CDSP的基本的运行逻辑为:外部的触发信号(比如输入的寄存器结果值更新)触发CDSP工作,CDSP计算完成,产生CDSP结果,并触发Tricore中断,由Tricore拿到CDSP结果值进行后续运算。

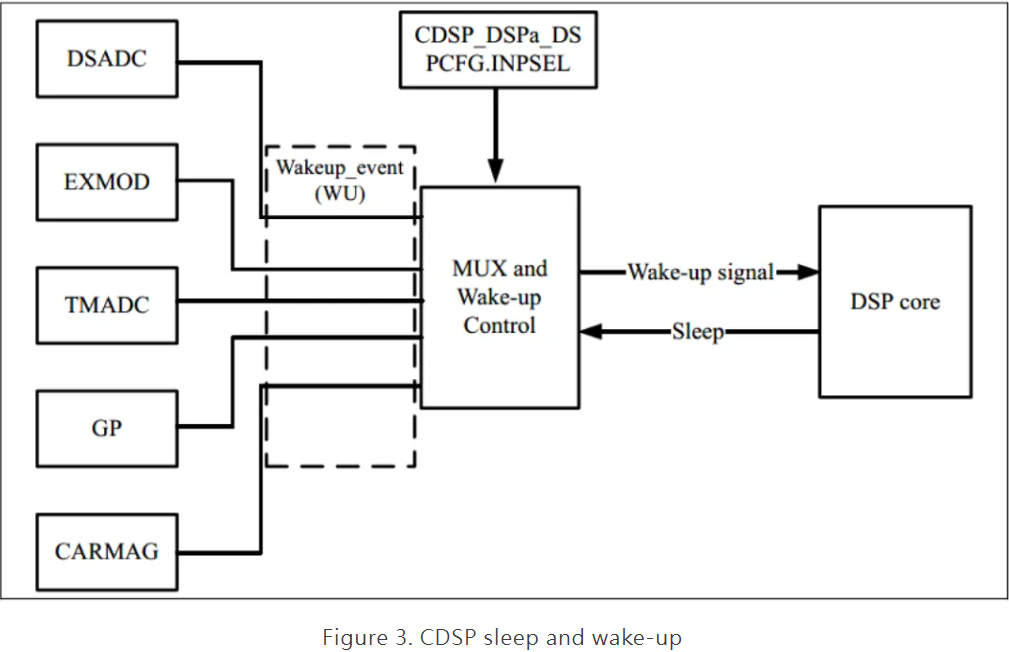

CDSP SW 正常工作下,CDSP 内核会交替处于休眠和唤醒状态,以处理输入采样。

在配置好输入信号源后(每次只能配置一个输入信号用于唤醒),当CDSP 内核接收到新的输入采样时,就被唤醒并转换到唤醒状态,以处理新的输入采样,处理完成后,生成结果到结果寄存器,然后再进入休眠。

CDSP_DSPa_DSPCFG 寄存器中的 INPSEL 位选择哪个输入采样到达会唤醒 CDSP 内核。例如,如果将 DSADC0 配置为 CDSP 内核的唤醒源,那么每个新的 DSADC0 输入采样都将唤醒 CDSP 内核。一旦 CDSP 内核被唤醒,它就会开始执行加载的滤波器链 (FC),直到产生结果到结果寄存器,CDSP 内核便进入休眠状态。

新输入采样的到来会再次唤醒 CDSP 内核,并重复上述过程。如果在 CDSP 内核仍在处理当前样本时(CDSP 内核仍处于唤醒状态),有新样本到来,则会产生唤醒错误。所以,用户使用时需要注意选择的滤波器链对一个输入样本的处理时间必须小于两个连续输入样本之间的时间间隔。

CDSP SW 的执行主要分为三个阶段:

启动

在启动阶段,CDSP 内核处于停止状态,CDSP SW 代码被复制到 ICCM 中,并将CDSP SW 的配置参数复制到DCCM 存储器中。

运行时:初始化

一旦 CDSP 内核从停止状态转换到运行状态,CDSP SW 就开始执行。CDSP SW 执行的第一阶段称为 "初始化",只执行一次。

在这一阶段,CDSP 滤波器链的所有配置参数都被初始化,CDSP SW 准备好处理输入采样。在这一阶段结束时,CDSP 内核转入休眠状态,等待输入采样到达配置的输入源。如果存在配置参数无效,CDSP将进入错误状态(死循环)。

运行时:主循环

每当有新的采样到达配置的 CDSP 输入源,就会触发唤醒事件,将CDSP 内核从休眠状态唤醒。唤醒后,CDSP 内核开始执行滤波器链,从而对输入信号进行处理。

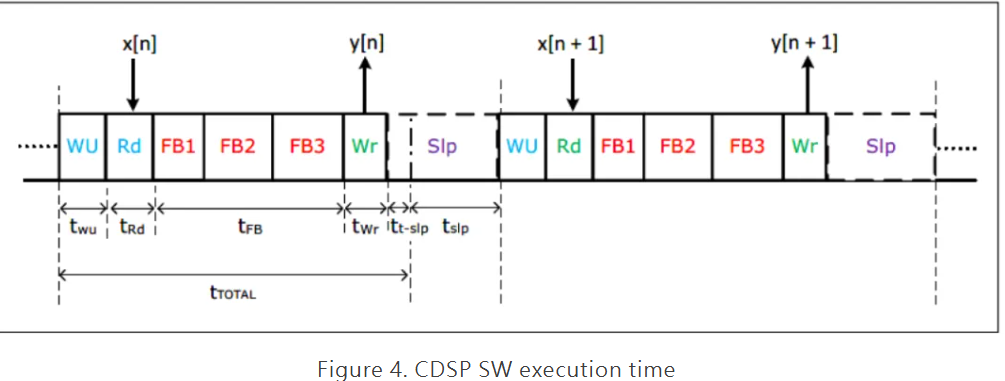

下图展示了一个通用 FC (Filter Chain)的 CDSP SW 主循环执行序列,用于处理单个输入采样。

如下图所示,CDSP 内核在唤醒 (t_wu)、读取输入采样 (t_Rd)、写入输出采样 (t_Wr) 和过渡到休眠状态 (t_t-slp) 的时间消耗都是固定数量的时钟周期 ,与 CDSP SW 配置无关,而滤波器块执行时间(t_FB)取决于滤波器链的配置。

例如,在中值滤波功能中,滤波执行时间(t_FB)会随着中值滤波器滤波器长度的增加而增加。用户需要确保一个输入采样的总执行时间(t_TOTAL)不超过 CDSP SW 两个连续输入采样之间的持续时间,否则会进入错误状态。

CDSP SW对单个输入采样运算的总执行时间公式如下:

t_TOTAL = t_wu + t_Rd + t_FB + t_Wr + t_t-slp

CDSP执行完成滤波链路并将输出结果写入输出寄存器后,DSP 内核将转入睡眠模式,直到下一个唤醒信号到来。

CDSP SW 中实现了以下滤波器模块:

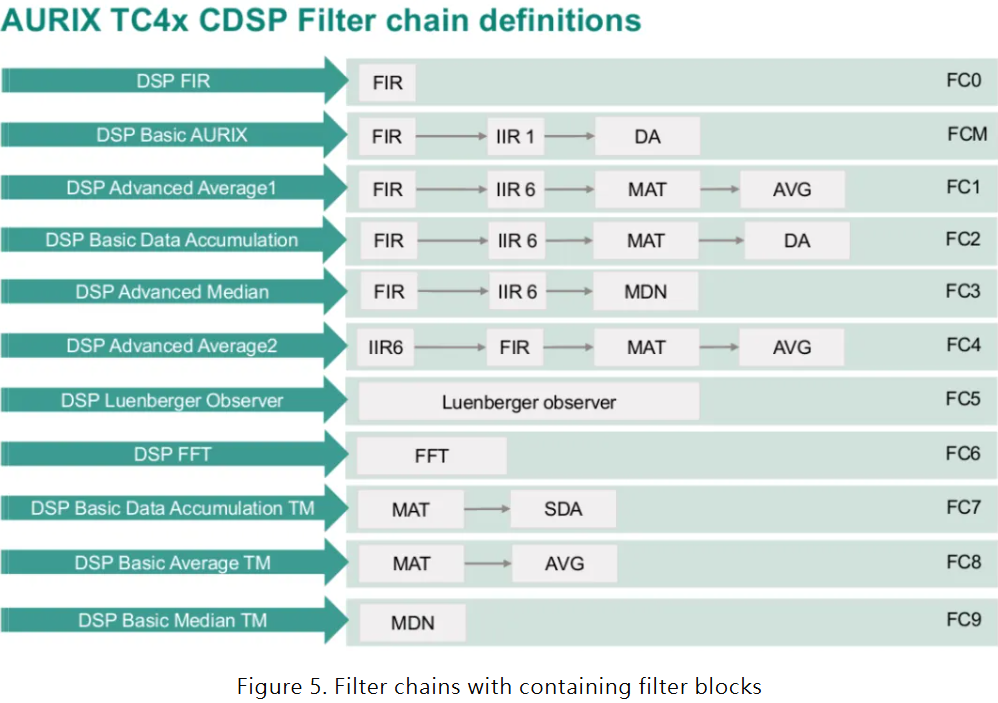

FCM,FC0-FC9共11个滤波链路是由上述滤波器组合形成的11个功能,如下图所示。

每一个CDSP可以选择其中任意一个滤波链路,并进行参数配置,应用于实际需求。

CDSP SW 通过可执行二进制文件提供,有 .bin、.hex、.h 和 .mem 4种格式,这些文件都包含相同的信息,用户根据需要选择文件格式进行集成。

除 FC5 滤波器链由两个单独的二进制文件实现外,其他各个滤波器链都由一个二进制文件实现。

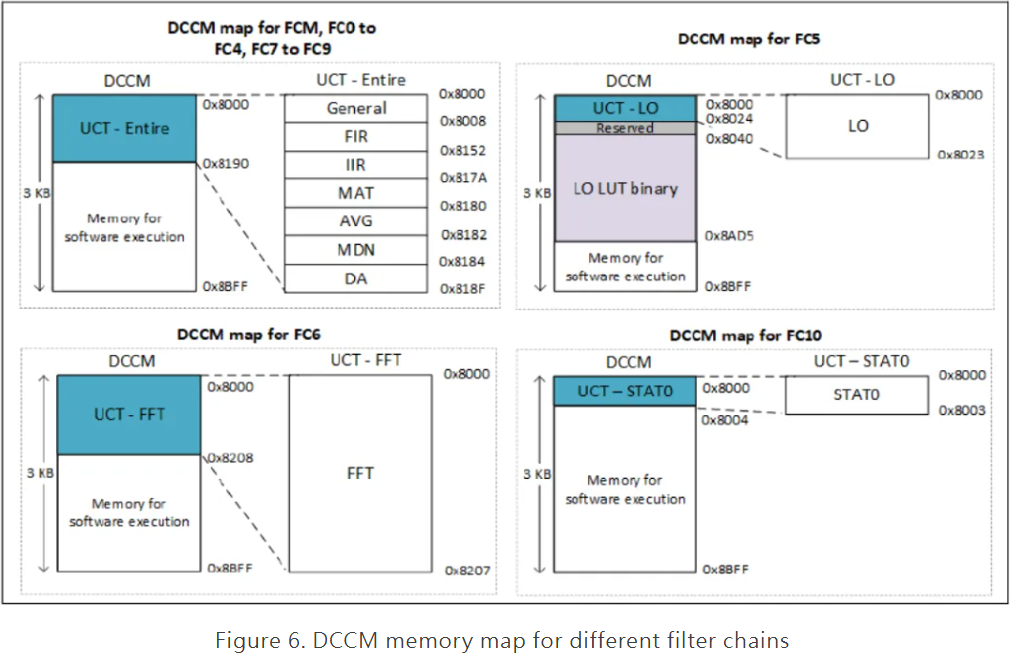

如图所示是一个DCCM参数配置表的示意图,有4种数据结构,根据选择的滤波功能不同,用户实例化其中一个数据结构并对关联的参数进行配置,来实现特定功能。

用户在Tricore应用程序中实例化一个数据结构后,将其加载到 CDSP 的 DCCM 存储中,并将对应的二进制文件加载到 CDSP的 ICCM存储中,即完成了功能集成。在运行期间,一次只能在 ICCM 中加载和执行一个滤波器链。

CDSP SW的使用非常方便,只需要配置相应的参数,并将配置参数放置到DCCM,把对应的运算功能代码放到ICCM,启动CDSP即可得到结果。

这里以FC9(基础中值滤波功能)和FC7(数学运算)为例,介绍使用方法。

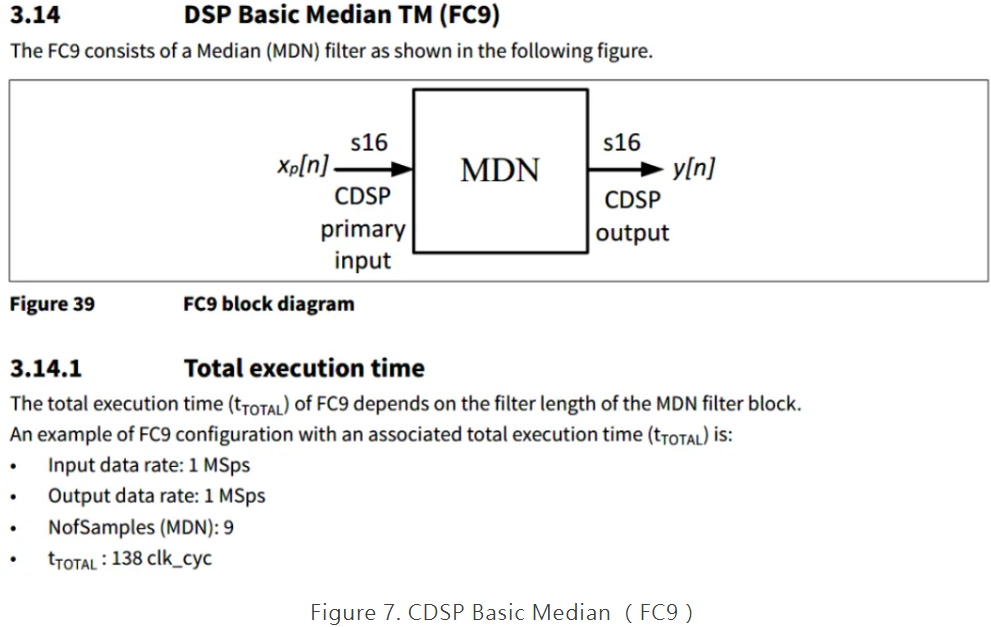

FC9的功能为计算几个输入信号的中值,计算速率可以达到1MSPs。

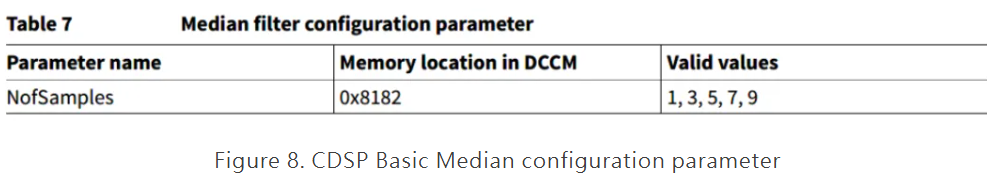

FC9的输入信号数量可以选1、3、5、7、9。

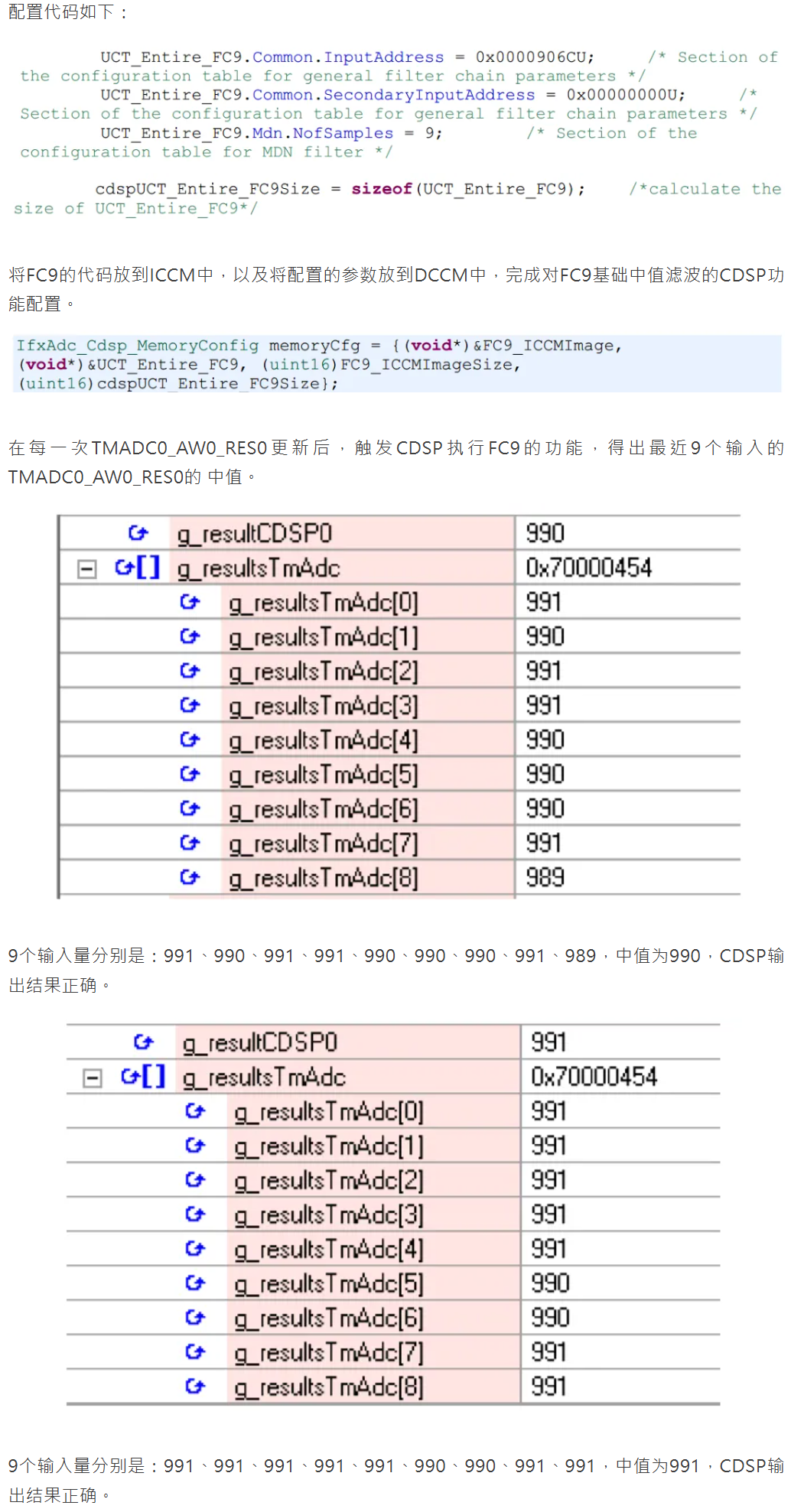

使用FC9功能,只需要设置CDSP的首位输入地址以及滤波信号长度,这里输入地址是0x0000906CU(映射地址为TMADC0_AW0_RES0),滤波信号长度为9。

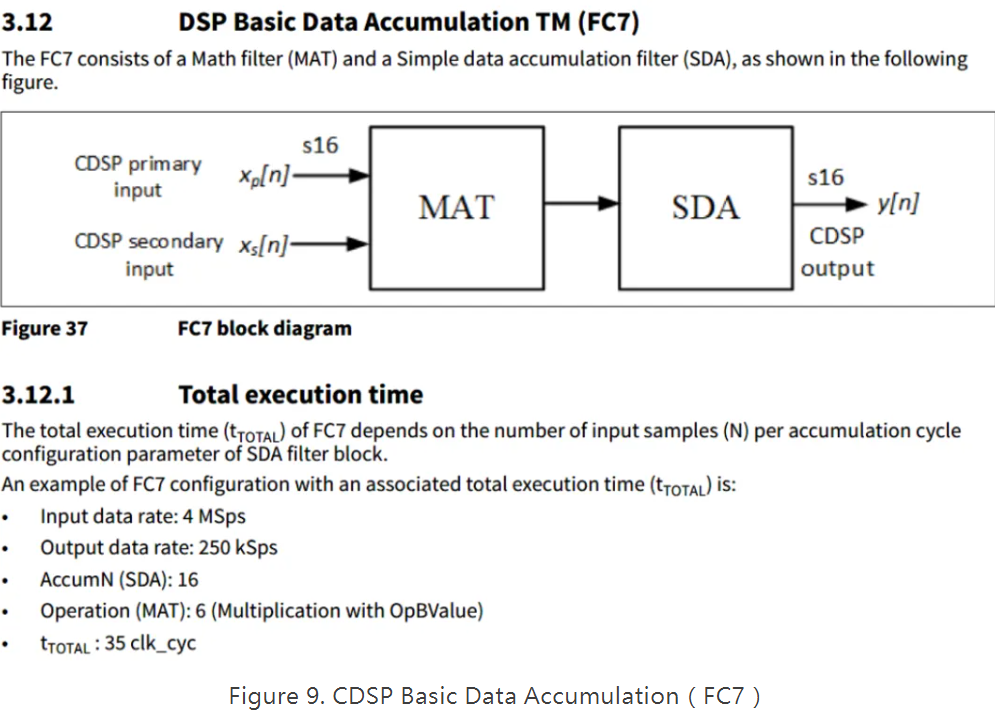

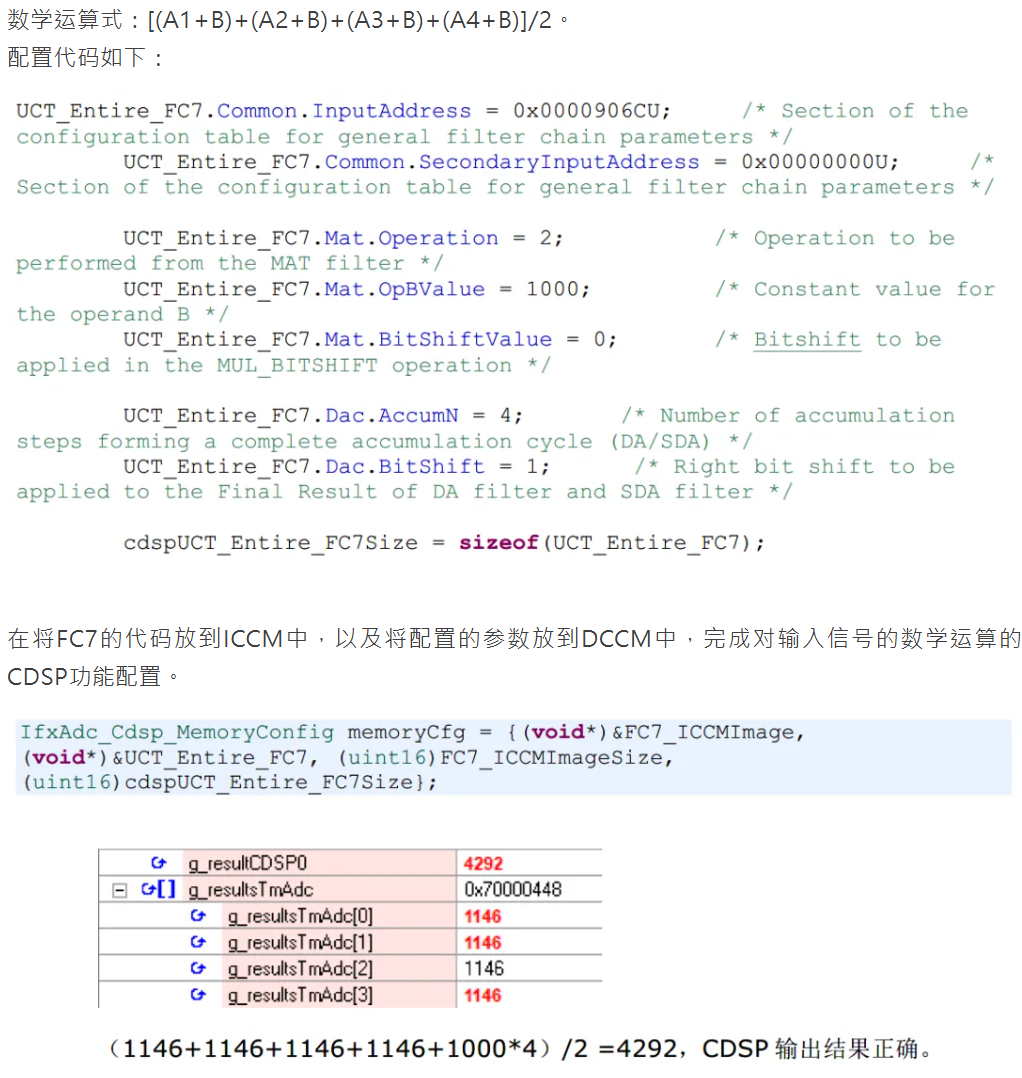

FC7的功能分为两个运行段,第一段是对输入的2个信号进行数学运算,第二段是将第一段的结果进行累加,两段都可以对各自的输出结果进行结果向右位移,即除法运算。

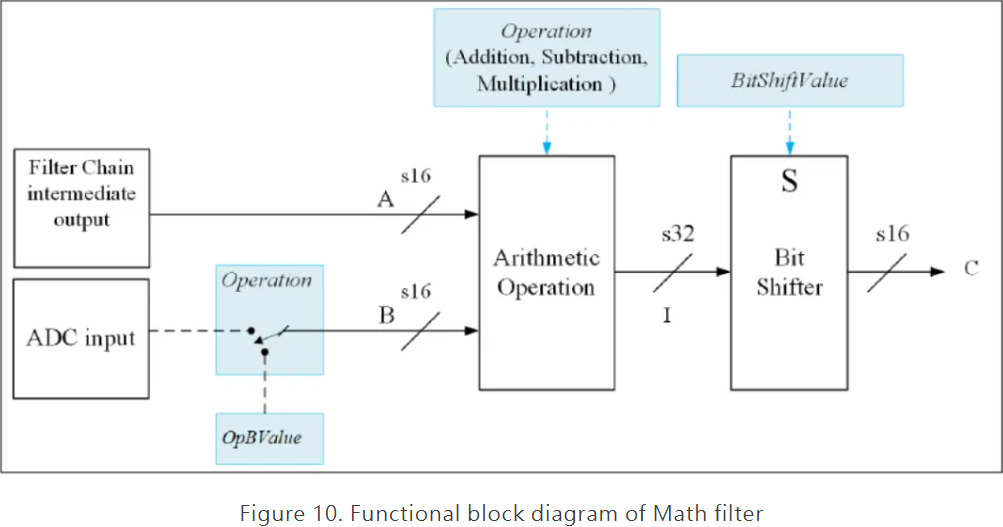

A和B进行运算,A为寄存器结果,B为寄存器结果或者为给定数值,A和B进行数学运算,并将结果进行位移。

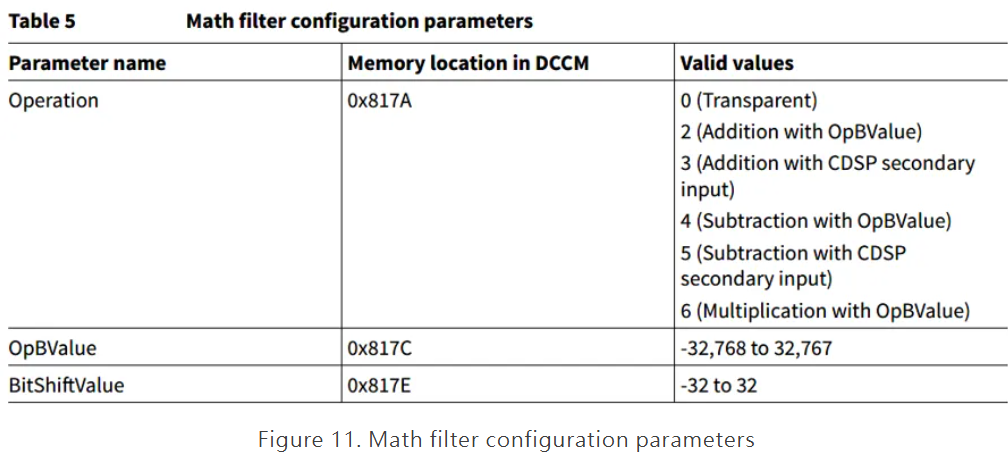

FC7的MAT部分参数说明,可以选择加、减、乘、除。

FC7的SDA部分参数说明,输入的信号数量可以是1-16,右移0-4位。

FC7的功能使用,只需要设置CDSP的首位输入地址,第二个输入参数,数学操作,累加运算信号数量,位移,这里首位输入地址是0x0000906CU(映射地址为TMADC0_AW0_RES0),第二个输入参数设置为固定值1000,数学运算为首位输入地址信号+第二个输入参数,累加运算长度为4,然后除以2,最终结果为平均值的2倍。

CDSP SW是英飞凌基于CDSP硬件模块开发的软件包,以二进制文件和头文件方式提供,使用便捷,功能丰富,可以用于旋变解码、发动机爆震、电压监测和滤波等场景。

CDSP SW的更多应用场景,有待广大用户去使用,欢迎大家点击 “英飞凌汽车电子生态圈” 最右边菜单 “AURIX™ 技术支持” 咨询使用。

REFERENCES

[1] Infineon-AURIX-TC4Dx-UM-v01_00-EN

[2] AURIX_TC4x_CDSP_PROD_V0.4.1-PR1_UserManual

[3] https://mp.weixin.qq.com/s/c1bjycblTr1oEyvPQWjQcg accessed on 20.11.2024 14:20 CST.